Monday, April 30, 2012

Altium Designer v10.1051.23878 | 3.12 GB

This summary is not available. Please

click here to view the post.

Saturday, April 14, 2012

Cadence SPB OrCAD 16.5.018 (Allegro SPB) Hotfix | 567MB

Cadence SPB OrCAD 16.5.018 (Allegro SPB) Hotfix | 567MB

Cadence OrCAD PCB design suites combine industry-leading, production-proven, and highly scalable PCB design applications to deliver complete schematic entry, simulation, and place-and-route solutions. With these powerful, intuitive tools that integrate seamlessly across the entire PCB design flow, engineers can quickly move products from conception to final output.

Cadence Design Systems is the worlds leading EDA company. Cadence customers use our software, hardware, and services to overcome a range of technical and economic hurdles.

New Allegro 16.5 Technology

The latest Allegro technology will be available through flexible on-demand product configurations that offer cost-efficiency and scalability. Allegro 16.5 spans silicon, SoC, and system-level development and offers PCB designers benefits such as:

- Higher functional density with a constraint-driven flow for embedded components

- Faster timing closure with new PCB interconnect design planning technology

- Fewer physical prototype iterations with concurrent team design authoring

- More efficient low-power design with integrated power delivery network analysis

- A compliant and faster implementation path with package/board-aware SoC IP

- Smoother collaboration among global teams with new SiP distributed co-design

- Flexibility through “base plus options” configurations

Fixed in Cadence SPB OrCAD 16.5.018

DATE: 03-16-2012 HOTFIX VERSION: 018

758924 PDN_ANALYSIS PCB_STATICIRDROP IRDrop via current report with flag for over current

903166 PSPICE FRONTENDPLUGIN Pspice > View netlist not working if .NET is assiciated with Capture

947680 PSPICE FRONTENDPLUGIN Out file is not displayed with view output file option in Win 7

951483 CAPTURE GEN_BOM SYLK File format is not valid in Excel

954330 CAPTURE GEN_BOM Corrupt BOM for attached design. How can we correct it ?

964000 CAPTURE NETLIST_OTHER User Defined Footprint getting replaced by value in Other netlist

968261 CAPTURE NETGROUPS Refdes Control required with Netgroup blocks

968345 CAPTURE NETGROUPS Cannot tick in the Place Netgroup window

974894 CAPTURE DATABASE Capture crashes when updating part from database

977355 ALLEGRO_EDITOR DATABASE Presence of fillets causing no such child error during add connect.

978007 ALLEGRO_EDITOR PCAD_IN PCAD Translation failure

978382 CAPTURE SCHEMATICS Placing testpoint symbol causes extra junction

978522 SIG_INTEGRITY LICENSING Q- Is there a way to set via model option in Orcad PCB Designer Professional license?

979041 SIG_INTEGRITY LIBRARY Contents of model_pcbsi.ndx were constantly accumulated when doing the distribution on each time

979594 CONSTRAINT_MGR CONCEPT_HDL Extra and incorrect information dumped in the alias conflicts reported generated from DE HD-CM Audit

981621 ALLEGRO_EDITOR DRC_CONSTR Updating DRC fails to set Shape Out of Date after changing NetClass membership that affects spacing

983608 F2B BOM Generating all variant BOMs changes selected variant

983629 SIG_EXPLORER EXPORT No exported cross section file created in directory with spaces

984218 CONCEPT_HDL INFRA Uprev from 162 > 165 causes certain ECSets to be in an illegal conflict state which is false

984578 F2B DDBPI PDV and con2con crash on part having illegal data into ptf view

984768 APD SHAPE Dynamic shape finishing with strange void.

985346 SIP_LAYOUT IMPORT_DATA import netlist-in-wizard fails and crashes

985451 APD DIE_GENERATOR die text in results in Invalid object type passed to GetPadstackLayer

986268 ALLEGRO_EDITOR GRAPHICS Copy & Move graphics issue with OpenGL

986552 ALLEGRO_EDITOR EDIT_ETCH The Cline is not avoided the "Route Keepout" by hug in 165. but it does in 16.3

986704 ALLEGRO_EDITOR EDIT_ETCH PCB Editor crashes during add connect

986895 ALLEGRO_EDITOR NC Any layer back drill issues

987309 SIP_LAYOUT COMPONENT_COMPAR Component Compare with DIA file and Net Assignment fails on co-design die with net assignment done by scm

987339 CONCEPT_HDL INFRA replace component inconsistent in .dcf file

987455 ALLEGRO_EDITOR DRC_CONSTR Allegro wrongly reporting Mechanical Pin Antipad to Pin Spacing drc

987669 ALLEGRO_EDITOR DRC_CONSTR multi-thread update DRC causes the application to crash

987843 SPIF OTHER Fanout vias on BOTTOM Layer are shown on TOP Layer in Allegro after routing and importing a session file from SPECCTRA.

988001 CONCEPT_HDL CONSTRAINT_MGR Cant assign Xnet to Electrical class at all and CM crashes if Ecset is assigned to xnet

988133 SIG_INTEGRITY OTHER Extra pin pairs are created in Prop Delay worksheet when ECSet is assigned to diff pair

988609 SIP_LAYOUT SYMB_EDIT_APPMOD When using the Symbol Applicatoin mode to edit a BGA the pin pitch settings are incorrect.

989078 ALLEGRO_EDITOR OTHER Export IDFs total thickness is not correct

Name: Cadence SPB OrCAD

Version: 16.5.018 (Allegro SPB) 32bit Hotfix

Creator: cadence.com

Interface: english

OS: Windows XP / Vista / Seven

Platform: Cadence SPB/OrCAD 16.50.000 - 16.50.017

OS: Windows XP / Vista / Seven

Download:

http://shareflare.net/download/80896.82cf647fffc8b3a74ae23de6ef12/rCAD.16.5.018_Snorgared.part1.rar

http://shareflare.net/download/29810.23b15806bfe6746fc0767d131111/rCAD.16.5.018_Snorgared.part2.rar

http://shareflare.net/download/56015.5ac66a8c5ef631b5ddf47c99f6df/rCAD.16.5.018_Snorgared.part3.rar

Mirror 1 :

http://letitbit.net/download/88315.82cf647fffc8b3a74ae23de6ef12/rCAD.16.5.018_Snorgared.part1.rar

http://letitbit.net/download/21633.23b15806bfe6746fc0767d131111/rCAD.16.5.018_Snorgared.part2.rar

http://letitbit.net/download/57541.5ac66a8c5ef631b5ddf47c99f6df/rCAD.16.5.018_Snorgared.part3.rar

Monday, April 9, 2012

Mentor Graphics Expedition Enterprise Flow EE7.9.3 + DMS7.9.3 x86 | 2.01 GB

Mentor Graphics Expedition Enterprise Flow EE7.9.3 + DMS7.9.3 x86 | 2.01 GB

Designing a product requires more than just a great PCB layout tool - you need tightly integrated PCB design software. Expedition Enterprise provides this high level of integration, enabling all team members to work collaboratively and more efficiently.

Meets the needs of mid-sized to large electronics companies with complex PCB designs

Eliminates the burden of managing multiple tools, with its common database and user interface

Supports globally dispersed design teams with real-time collaboration

Maintains data integrity - from concept to manufacturing

Reduces design cycle time and manufacturing costs, while increasing productivity

Integration

As an Expedition Enterprise project evolves from concept to finished product, the database is always synchronized, notifying the engineer and designer of changes as they occur, eliminating unnecessary and costly design iterations.

Expedition Enterprise is integrated with DMS� (Data Management System) and CES (Constraint Editing System), providing a central infrastructure for component libraries, design data versioning and management, design reuse, where used, entry and management of high speed and manufacturing rules, and integration with corporate PLM systems.

Once the design is complete, integration with manufacturing output tools ensures that the integrity of the design is maintained, even when your teams are globally dispersed.

Mirror 1

http://shareflare.net/download/48402.45853d8808181ab8fd8978838297/MG_EE7.9.3.part1.rar.html

http://shareflare.net/download/67546.64a9b6b86181823ad5e1fda386f6/MG_EE7.9.3.part2.rar.html

http://shareflare.net/download/35738.399984e6cf0b606c7822210ed757/MG_EE7.9.3.part3.rar.html

http://shareflare.net/download/04797.0925b2faa52d6e96ac910249a74e/MG_EE7.9.3.part4.rar.html

http://shareflare.net/download/83440.8e831eedef983305951a7b68d882/MG_EE7.9.3.part5.rar.html

http://shareflare.net/download/52884.5aa4a078f476d4680f62405ca1b1/MG_EE7.9.3.part6.rar.html

http://shareflare.net/download/48402.45853d8808181ab8fd8978838297/MG_EE7.9.3.part1.rar.html

http://shareflare.net/download/67546.64a9b6b86181823ad5e1fda386f6/MG_EE7.9.3.part2.rar.html

http://shareflare.net/download/35738.399984e6cf0b606c7822210ed757/MG_EE7.9.3.part3.rar.html

http://shareflare.net/download/04797.0925b2faa52d6e96ac910249a74e/MG_EE7.9.3.part4.rar.html

http://shareflare.net/download/83440.8e831eedef983305951a7b68d882/MG_EE7.9.3.part5.rar.html

http://shareflare.net/download/52884.5aa4a078f476d4680f62405ca1b1/MG_EE7.9.3.part6.rar.html

Mirror 2

http://ul.to/xjkagjdx/MG_EE7.9.3.part3.rar

http://ul.to/polcgu67/MG_EE7.9.3.part5.rar

http://ul.to/eli49zcz/MG_EE7.9.3.part2.rar

http://ul.to/23dx2a18/MG_EE7.9.3.part6.rar

http://ul.to/vlznfcld/MG_EE7.9.3.part4.rar

http://ul.to/dgibdf80/MG_EE7.9.3.part1.rar

http://ul.to/xjkagjdx/MG_EE7.9.3.part3.rar

http://ul.to/polcgu67/MG_EE7.9.3.part5.rar

http://ul.to/eli49zcz/MG_EE7.9.3.part2.rar

http://ul.to/23dx2a18/MG_EE7.9.3.part6.rar

http://ul.to/vlznfcld/MG_EE7.9.3.part4.rar

http://ul.to/dgibdf80/MG_EE7.9.3.part1.rar

Mirror 3

http://turbobit.net/9axnlif0glcu/MG_EE7.9.3.part1.rar.html

http://turbobit.net/mgf883frog7i/MG_EE7.9.3.part2.rar.html

http://turbobit.net/dx1xowbo2bqi/MG_EE7.9.3.part3.rar.html

http://turbobit.net/x4uetosv1vx2/MG_EE7.9.3.part4.rar.html

http://turbobit.net/91k6arw7lseo/MG_EE7.9.3.part5.rar.html

http://turbobit.net/35zlgsz9u39s/MG_EE7.9.3.part6.rar.html

Thursday, April 5, 2012

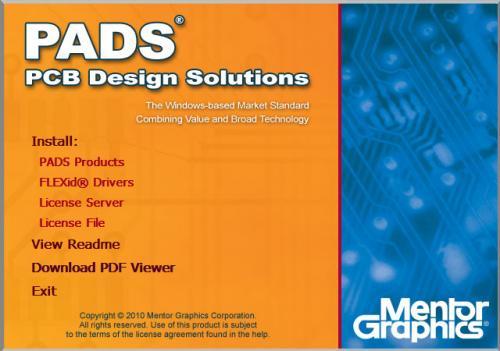

Mentor Graphics PADS 9.4.1 | 1.3 Gb

This summary is not available. Please

click here to view the post.

Wednesday, April 4, 2012

Altium Designer 10.972.23595 ENG/x64/x86 2012 | 3.15 GB

Altium Designer 10.972.23595 ENG/x64/x86 2012 | 3.15 GB

Information:-Altium Designer is an EDA software package for printed circuit board, FPGA and embedded software design, and associated library and release management automation. It is developed and marketed by Altium Limited of Australia.

Schematic capture module provides electronics circuit editing functionality, including:

Component library management

Schematic document editing (component placement, connectivity editing and design rules definition)

Integration with several component distributors allows search for components and access to manufacturer's data

SPICE mixed-signal circuit simulation

Pre-layout signal integrity analysis

Netlist export.

Reporting and BoM facilities.

Multi-channel, hierarchical schematics and design re-use

Printed circuit board design module of Altium designer allows:

Component footprint library management

Component placement

Manual trace routing, with support for differential pairs, multi-trace routing, pin-swapping and gate-swapping

Automatic trace routing

Automated multi-channel layout and routing

Interactive 3D editing of the board and MCAD export to STEP

Signal integrity analysis

Manufacturing files generation with support for Gerber and ODB++ formats

Mentor Graphics Pads 9.4.1 (x32/x64) | 1.41 GB

Mentor Graphics Pads 9.4.1 (x32/x64) | 1.41 GB

PADS, Mentor Graphics’ world-leading desktop PCB design tool, enables you to develop PCBs within a highly productive, scalable, and easy-to-use environment.

About Mentor Graphics

Mentor Graphics provides software and hardware design solutions that enable companies to develop better electronic products faster and more cost-effectively. We offer innovative products and solutions that help engineers overcome the design challenges they face in the increasingly complex worlds of board and chip design.

Overview

PADS, Mentor Graphics’ worldwide leading desktop PCB design solution, enables individuals and small teams to develop PCBs within a highly productive and easy-to-use environment. Integrated and scalable, PADS allows individual engineers and designers to accomplish a wide breadth and depth of core PCB development tasks, including schematic entry, analog design, signal and power integrity, thermal analysis, and PCB layout-to-manu-facturing preparation.

PADS offers a low cost of entry, yet delivers high performance that exceeds other desktop PCB design solutions on the market. Long a part of the Mentor Graphics PCB lineup, PADS has benefitted from continuous, solid development and global distribution, making it the most popular desktop PCB software package in the world. And, as a Mentor Graphics PCB solution, PADS provides a clear and connected path to an enterprise flow if your requirements grow.

Download:

http://netload.in/dateiaLMUtWJ3j2/Mentor_Graphics_PADS_9.4.1.rar.htm

http://sms4file.com/download/81222.80f4e38e9b405b59541d29ea37f8/Mentor_Graphics_PADS_9.4.1.rar.html

Subscribe to:

Comments (Atom)